Five-stage Pipelined ARM CPU

University of Washington, Seattle

09/2020 - 12/2020

Keywords: Computer Architecture | Verilog | SystemVerilog | ARM Assembly | Five-stage CPU | Instruction memory | Register file | ALUs

Role

Impacts

Skills

Descriptions

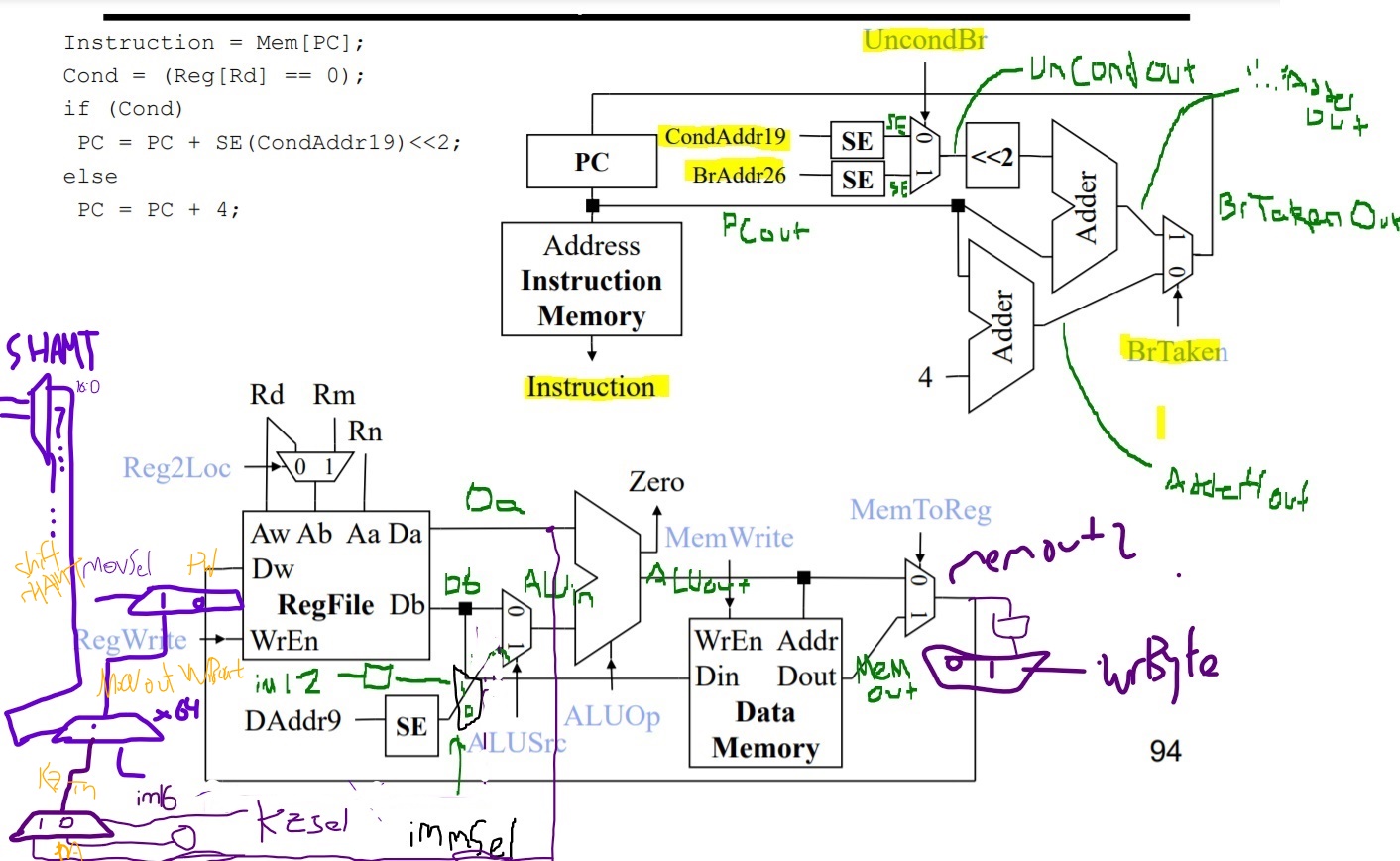

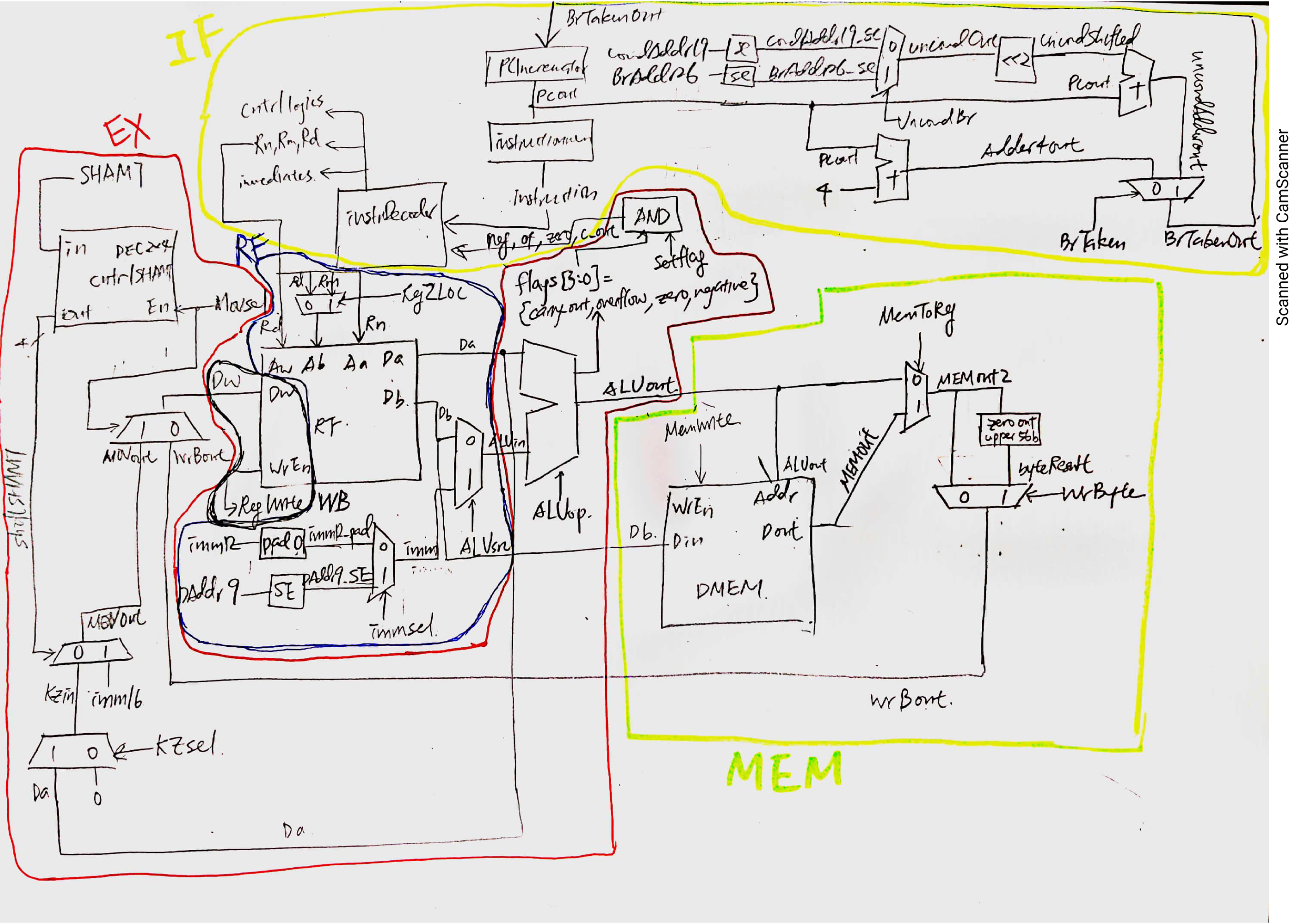

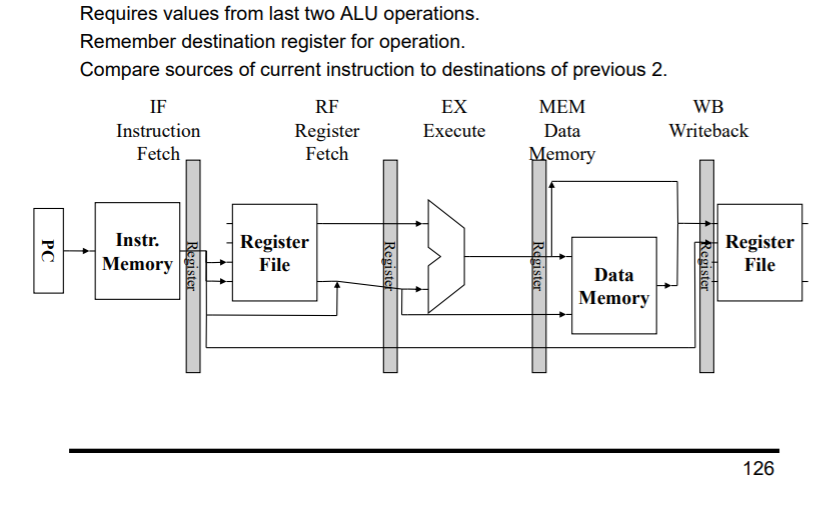

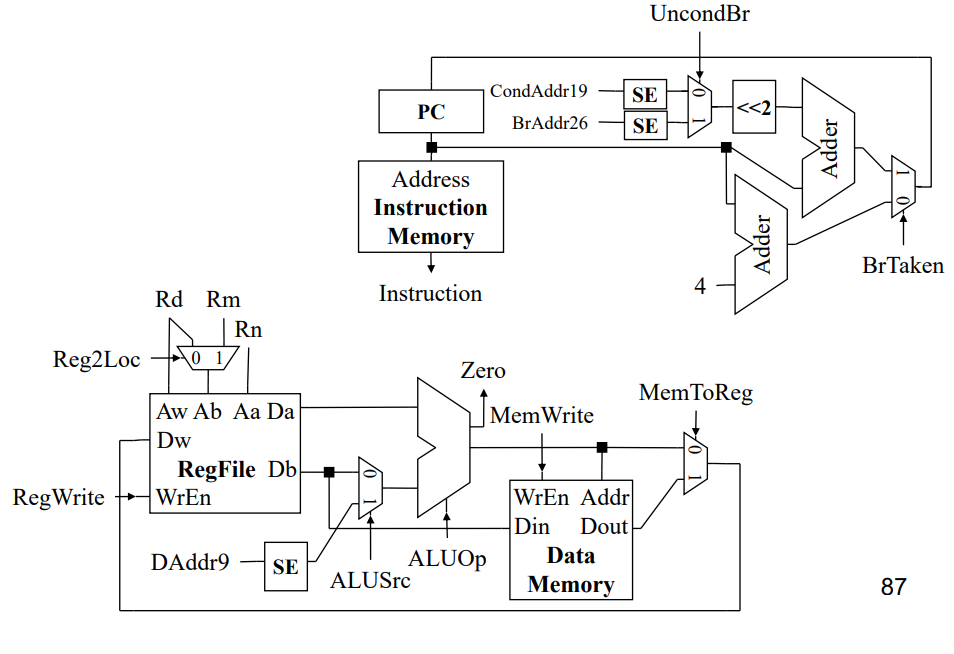

We designed a five-stage pipelined ARM 64-bit CPU using basic gates and multiplexers. The components include a instruction memory set, a program counter, a register file, a data memory, and a few ALUs. These components achieve reading a set of ARM assembly codes and translating to machine code, which can futher be used to triggers ALU operations on specified registers in the memory. The CPU is broken down into five-stages, making the throughput 5 times higher for each clock cycle.